Lo primero que se debe de hacer es seleccionar el flip-flop con el que se va a trabajar (en mi caso fue un tipo J-K), despues colocar las tablas de verdad de tal circuito.

las tablas se pueden ver en el siguiente enlace.

despues se realizaran las tablas de estado actual CBA y estado siguiente C*B*A*

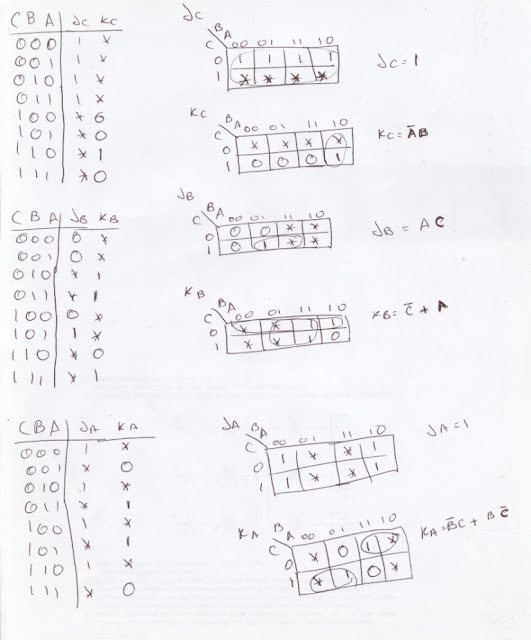

se realizaran los mapas para JA,KA JB,KB JC,KC que serán las entradas J y K de cada Flip-Flop como se puede ver en las siguientes imágenes.

1.- Sacar la tabla de verdad del flip flop J-K

2.- sacar la tabla caracteristica del flip-flop J-K

MATERIAL:

2 C.I 74LS109 (F.F J-K con Reset y Set)

1 C.I 74LS04 (Conpuerta inversora)

1 C.I 74LS08 (Compuerta NAN)

1 C.I 74LS32 (Compuerta OR)

1 C.I 74LS47 (Decodificador BCD a 7 segmentos)

1 Display de 7 segmentos Anodo comun.

1 Fuente de 5Vcc

A continuación se muestra las imágenes que se realizaron con en el simulador Proteus el cual representa un circuito contador sin crono Ascendente del 3 al 6 y se deja el enlace de la simulación por si en algún momento se necesita este mismo.

se colocaran imágenes con los pasos para realizar este circuito.